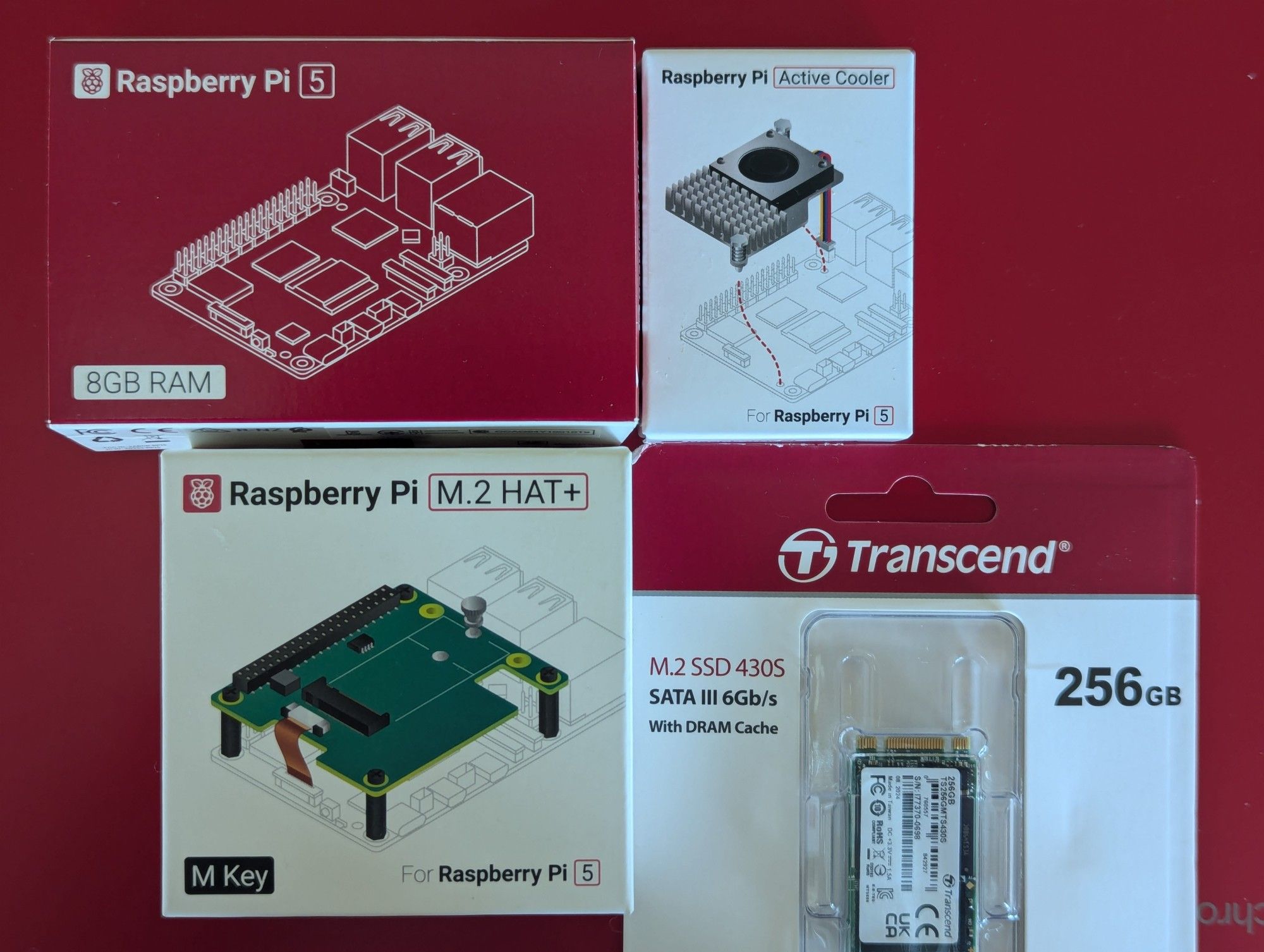

Got a fast ARM64 self-dev tool, because my homebrewed float80 library behavior on COrtex-M7 looks suspicious. It is also nice that long double on ARM64 linux is 128bit. There is no problem other than M.2/NVME doesn't work at all. Huh? Why?

時間が自由で良いですよぉ〰️

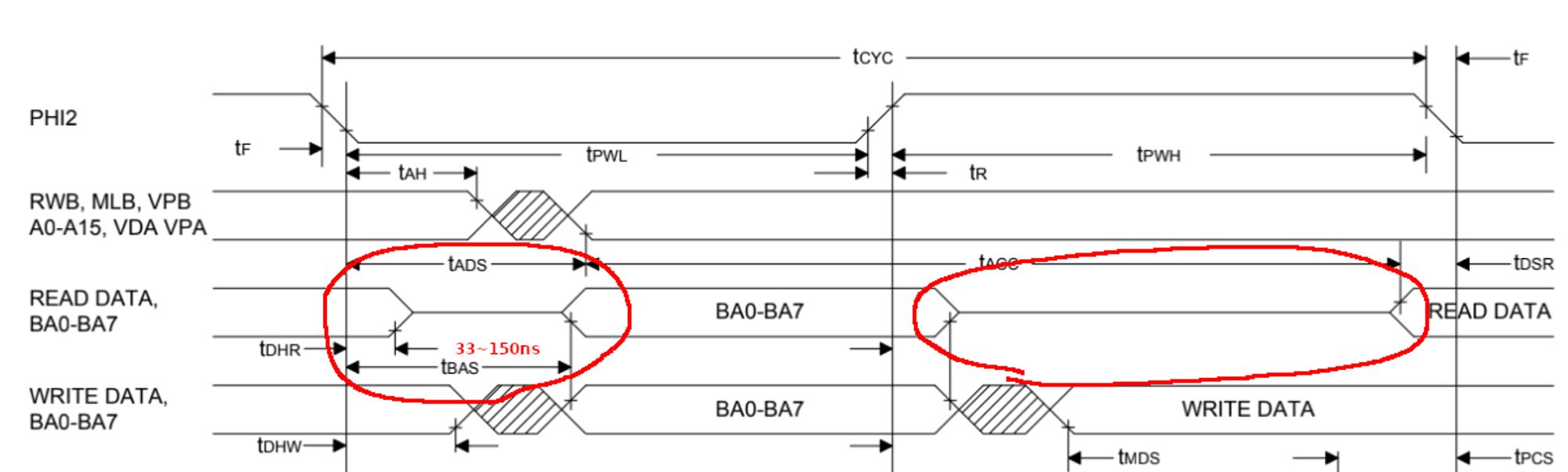

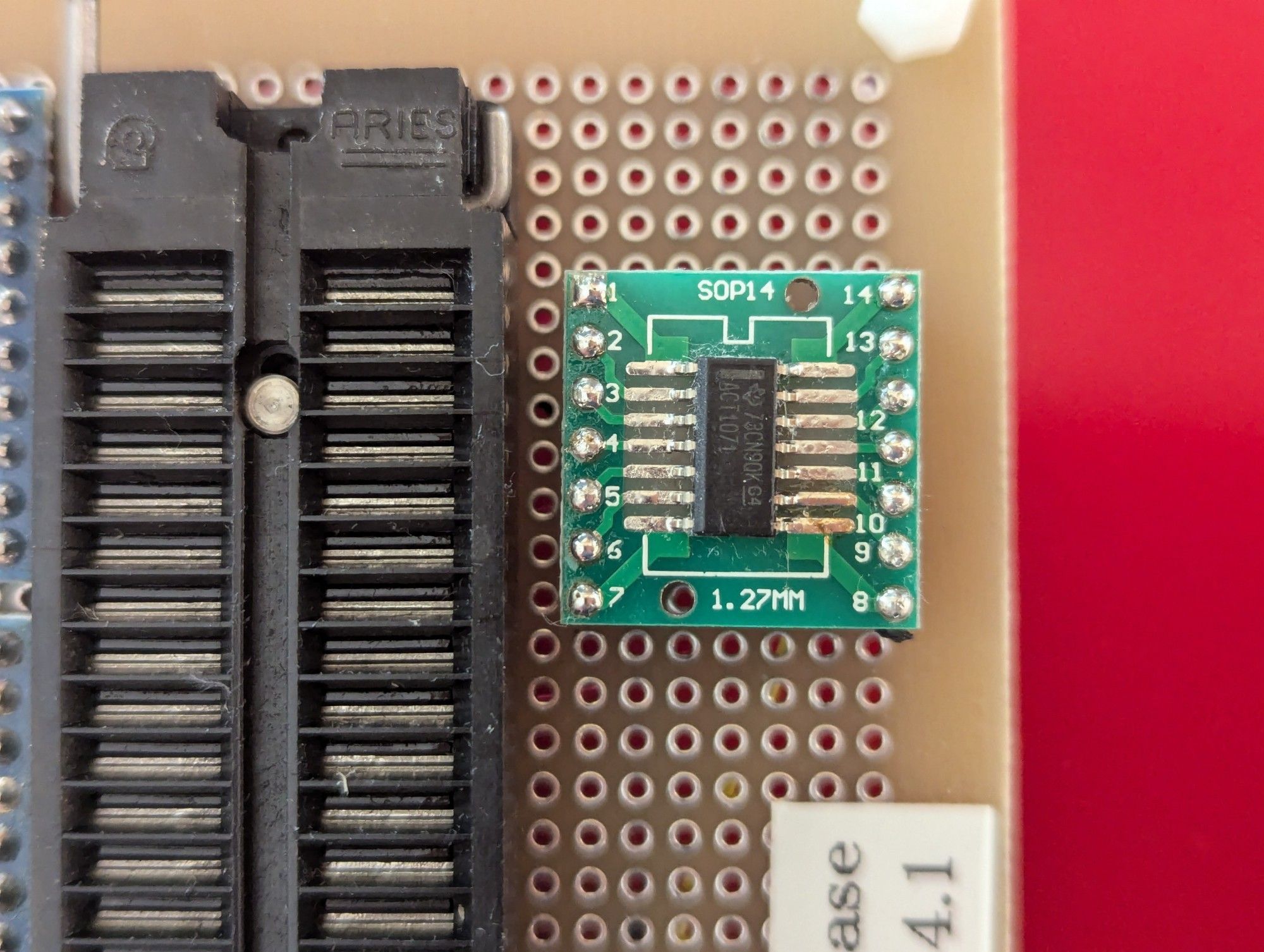

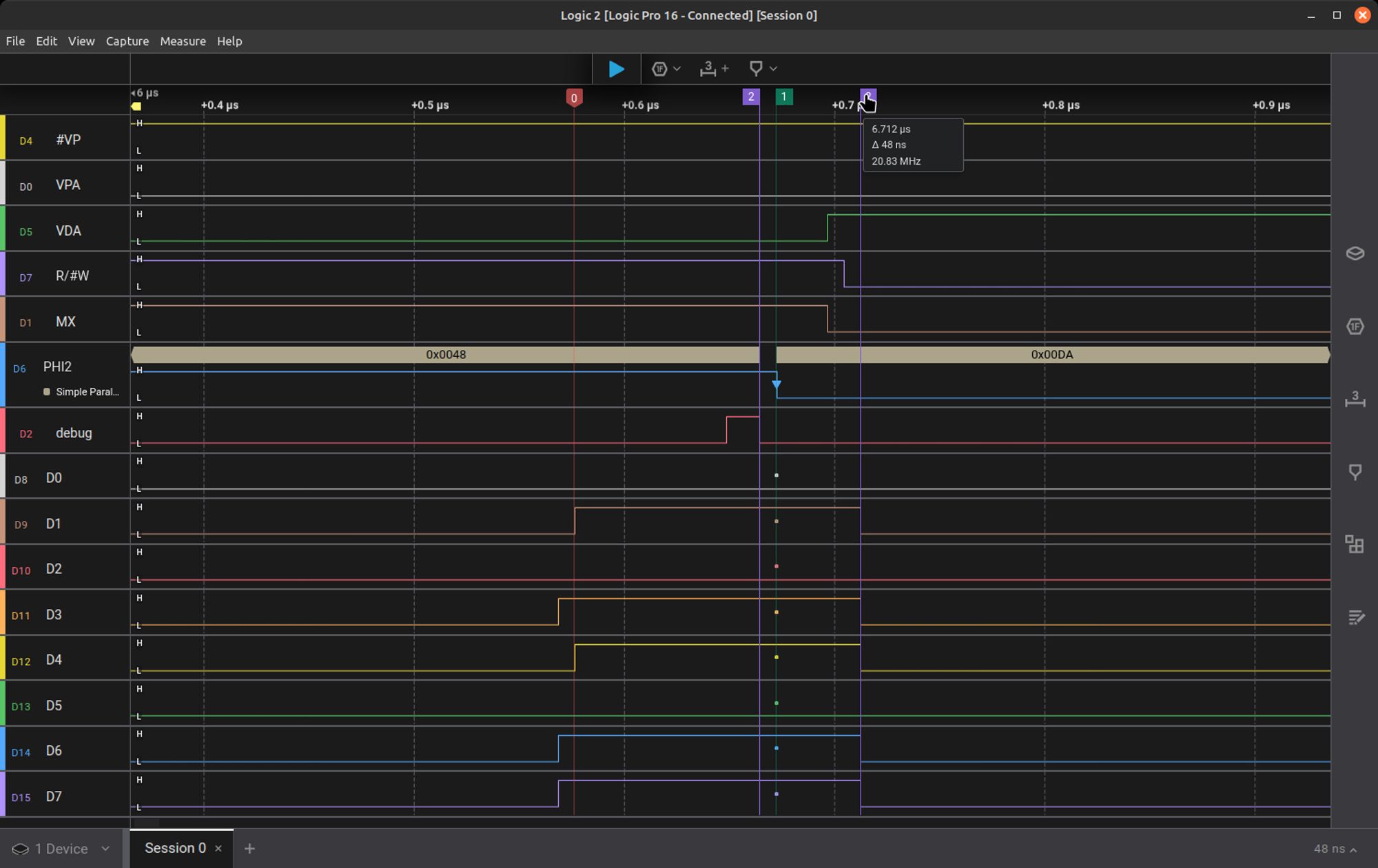

I installed a bus terminator SN74ACT1071 into multiplexed address-data bus of W65C816. The bus-hold function works as expected from 2-left to 2-right. 0) output data 2-left) switch to input 1) negate phi0 2-right) bank address output

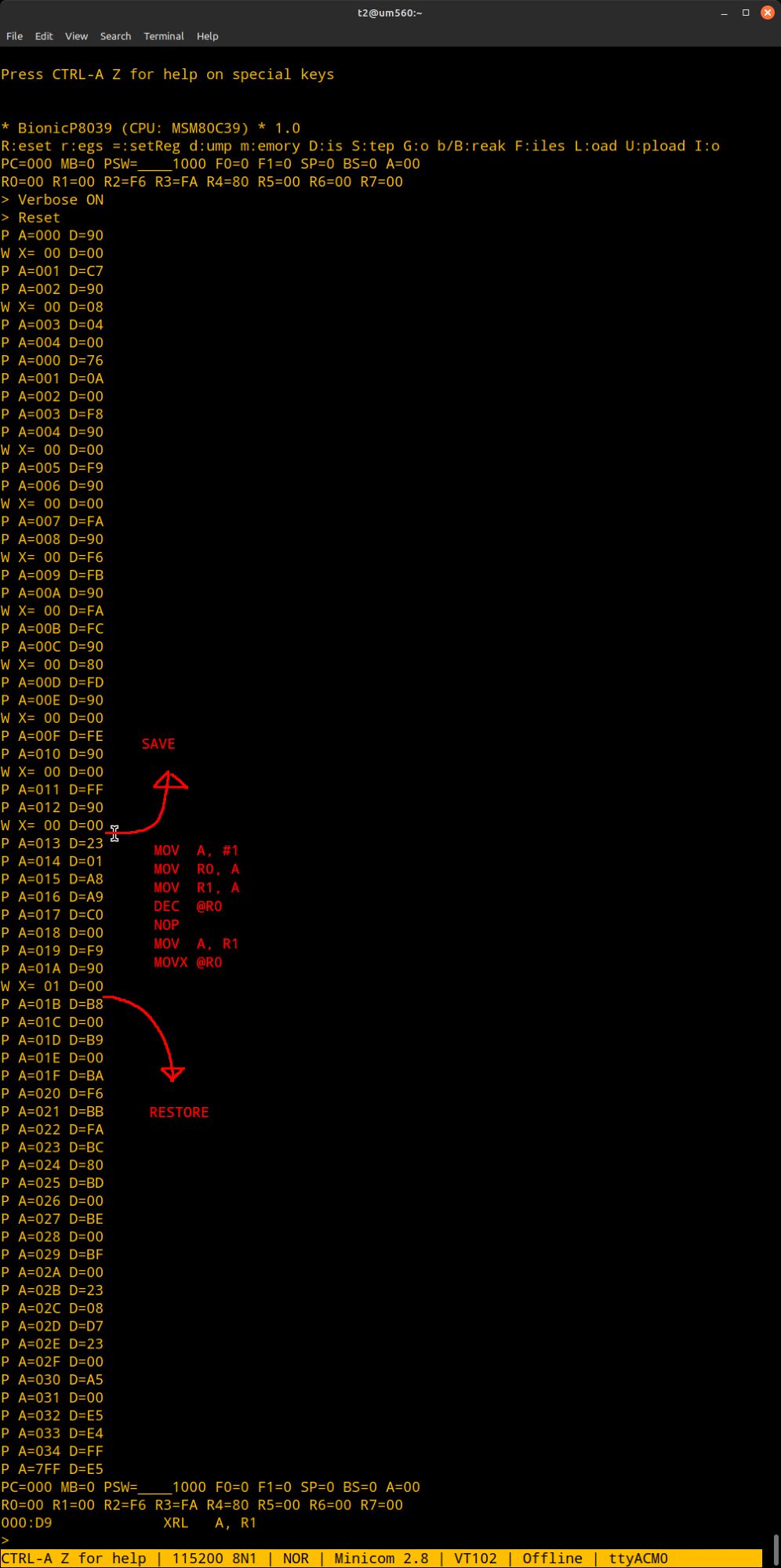

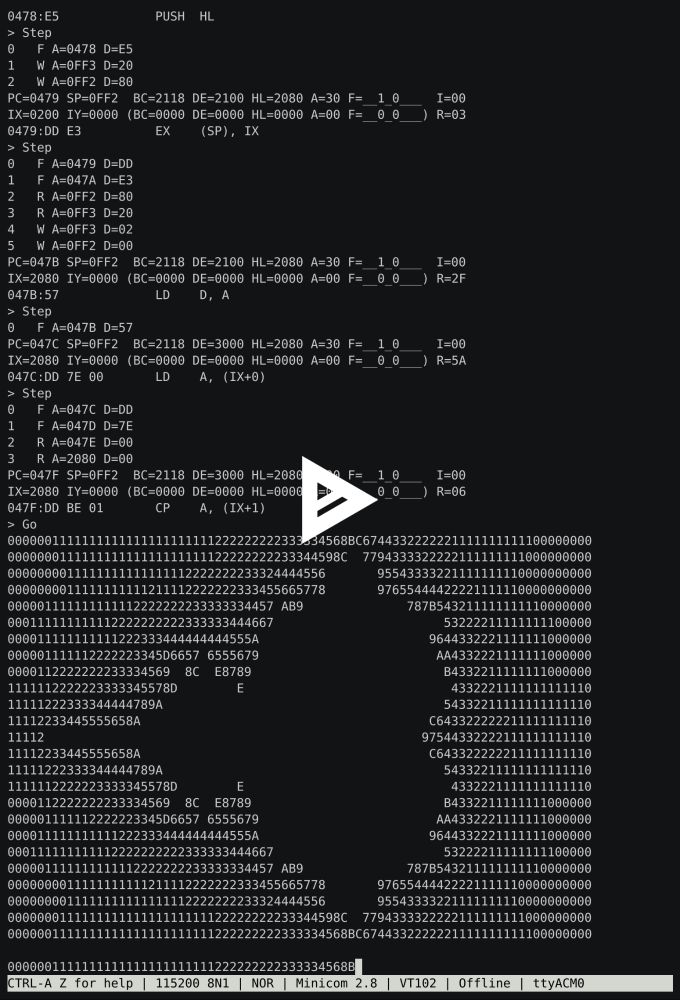

BionicZ80 implementation has done. It is easy to control 4MHz clock by Teensy 4.1. asciinema.org/a/661752#Z80 Next challenge might be NSC800.

Z80 can run at 4MHz clock using Teensy 4.1 as the controller. This recording demonstrates Mandelbrot Set drawing using 16-bit integer arithmetics routines written in assembly language. https://gith...

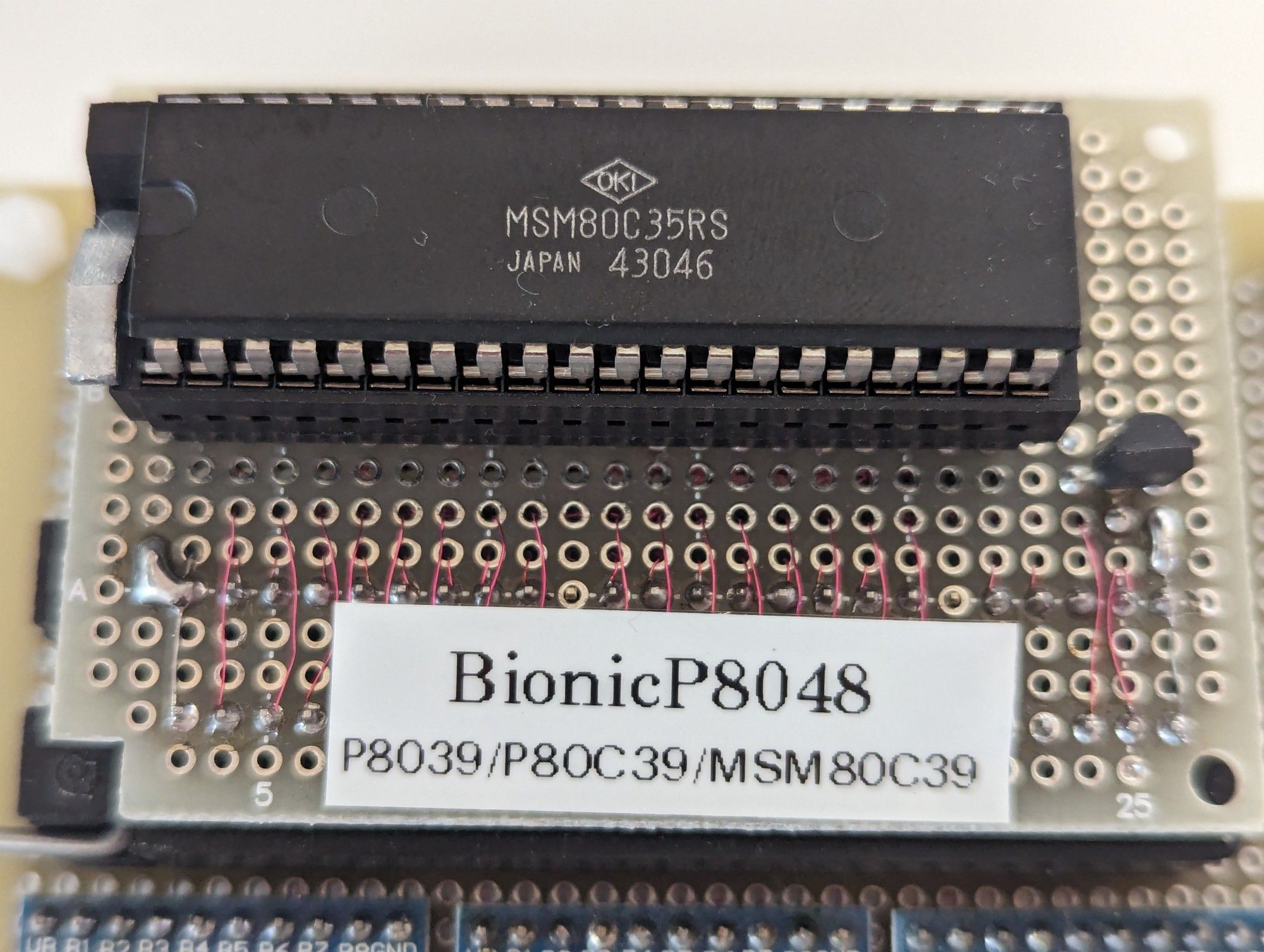

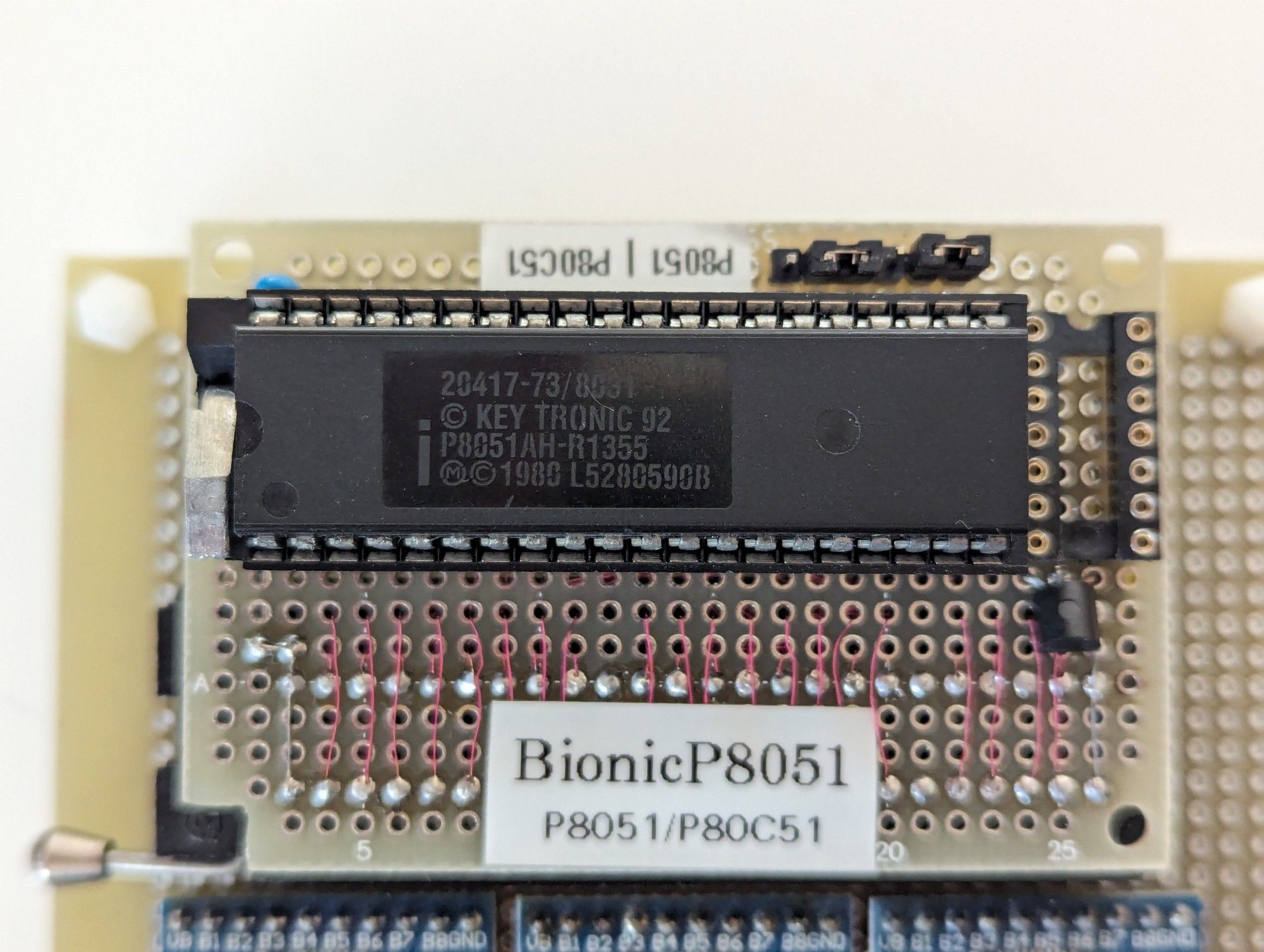

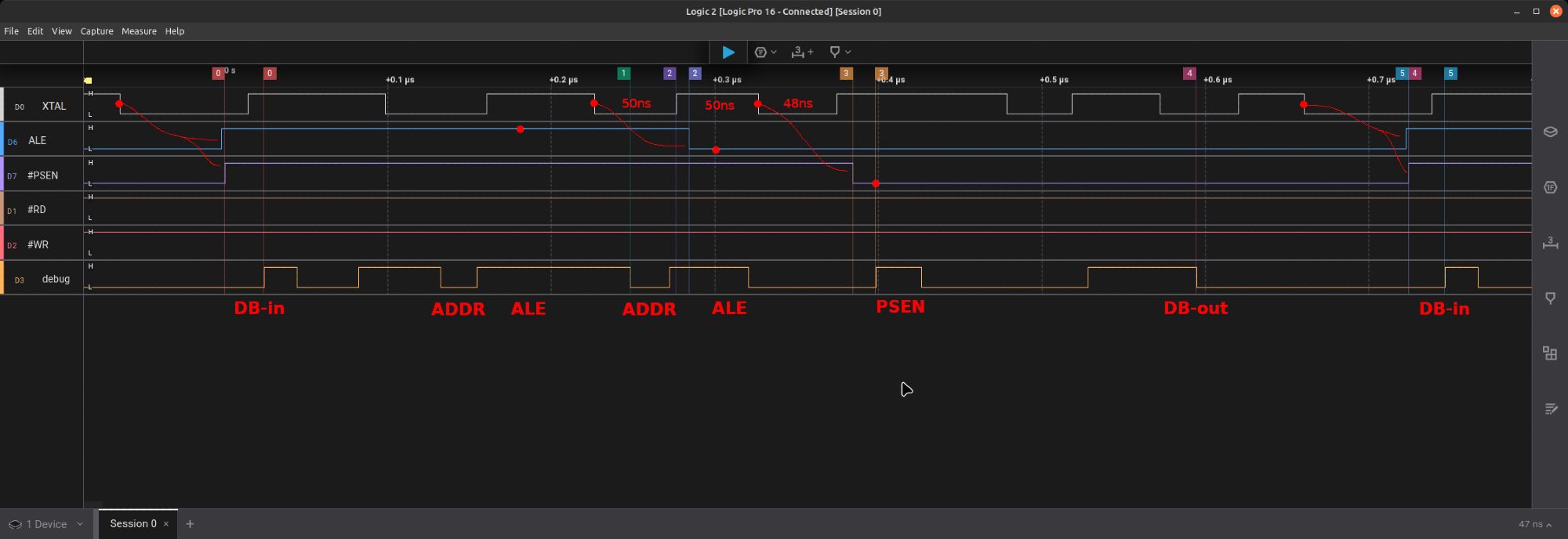

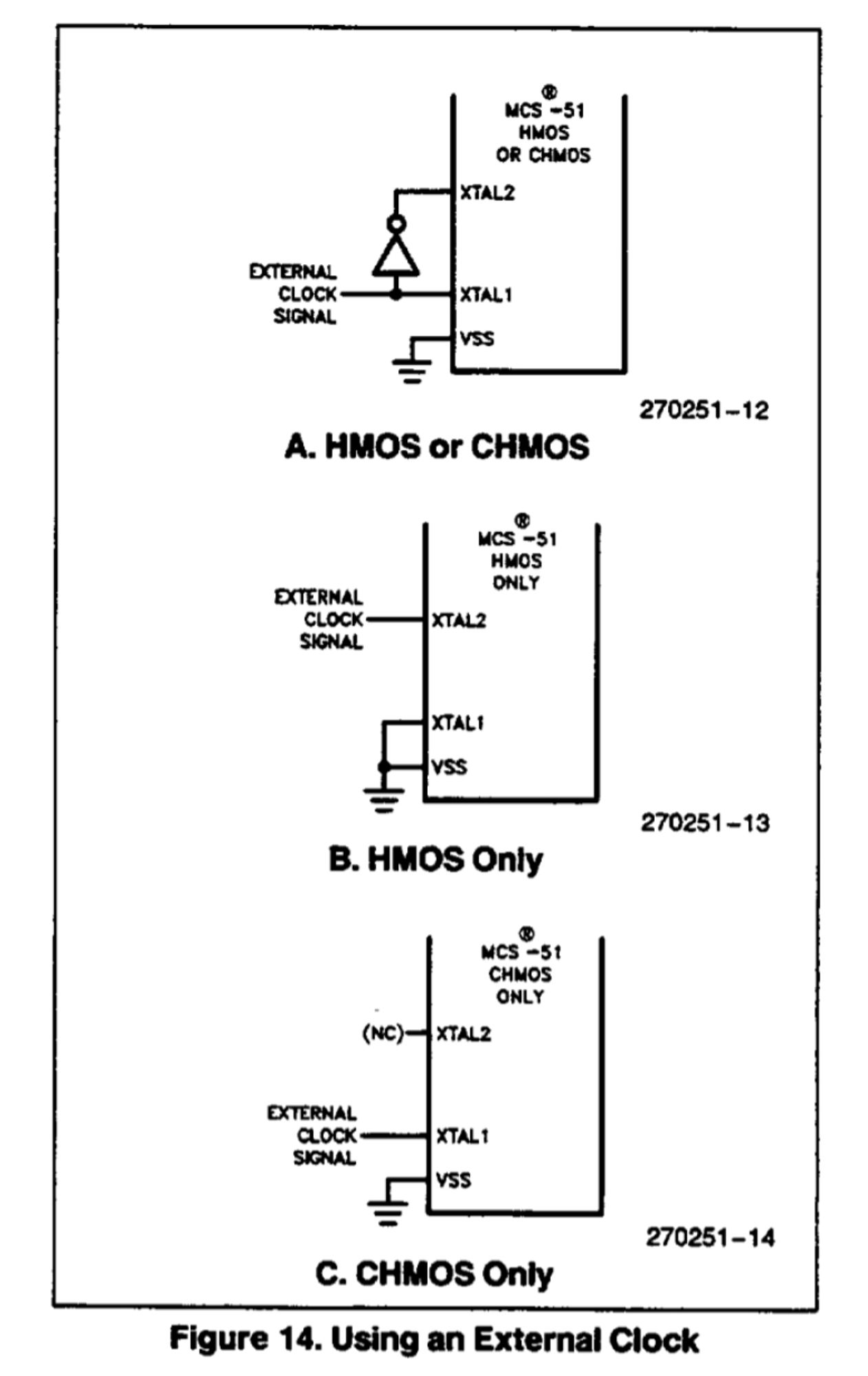

I'm playing with 8051, and now trying to tune with maximu clock 12MHz. A delay from clock edge to control signal is about 50ns which is near the half clock cycle, so that controling by software is quite difficult to tune. Also the phase of external clock differs between HMOS and CMOS.

A noise in 65816 native mode comes from a conflict between read data and bank address on data bus. I can delay a read data at PHI2=H but controll at PHI2=L is tough. Negate PHI2, keep tDHR, switch to input until tBAS, otherwise conflict happens. Try a workaround and running endurance test.