More Efficient Lattice-based OLE from Circuit-private Linear HE with Polynomial Overhead (Leo de Castro, Duhyeong Kim, Miran Kim, Keewoo Lee, Seonhong Min, Yongsoo Song) ia.cr/2024/1534

Bitwise Garbling Schemes — A Model with $\frac{3}{2}\kappa$-bit Lower Bound of Ciphertexts (Fei Xu, Honggang Hu, Changhong Xu) ia.cr/2024/1532

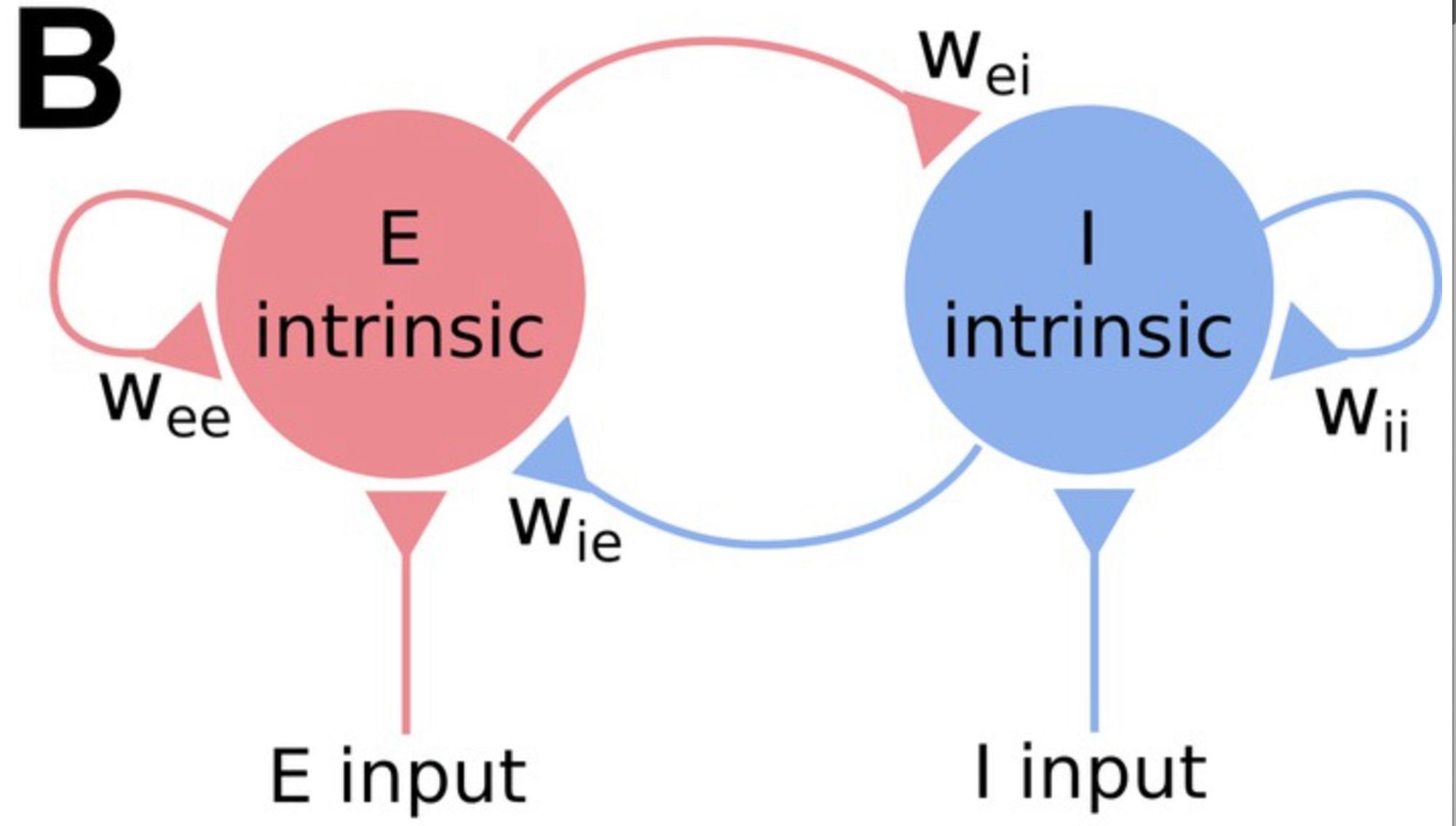

"Excitation/Inhibition imbalance" is a popular theory for brain disorders eg ASD & schizophrenia. Even a clinical trial for a GABA-B agonist in ASD (clinicaltrials.gov/study/NCT03...). But I just don't get it. In this diagram of an E-I circuit, which synapses count as excitatory vs inhibitory?

When did you do your stand up Graeme? Was it on the Scottish comedy circuit?

A metal shutter, buckling on Wesleyan brick, no light, no power. To whom is left this relic of the Methodist Circuit? (41/68, 'White Thorns', 2017)

AlphaChip: 강화학습(RL) 기반의 칩 배치 생성 방법에 대한 연구 (feat. Google) (by 9bow님) https://d.ptln.kr/5291 #google #ai-chip #reinforcement-learning #tpu #circuit-design #trilium #replace #edge-gnn #markov-decision-process #floorplan #alphachip

들어가며 :pytorch:🇰🇷 지난 9월 말 AlphaChip이라고 이름 붙인, 강화학습 기반의 칩 배치 생성 방법에 대한 짧은 추가 논문(Addendum)이 nature에 공개되었습니다. AlphaChip은 지난 2020년 공개된 강화학습(RL) 기반의 칩 설계 및 배치(Chip Design & Placement) 생성 방법에 대한 연구(A graph placement methodology for fast chip design)를 기반으로 하고 있으며, Google의 TPU 설계에 실제로 적용된 것으로 유명합니다. 이번에 추가된 논문(Addendum)에서는 사전학습을 활용한 효율성 증대를 비롯하여 초기 배치와 벤치마크 등에 대한 내용을 다루고 있습니다. 이러한 추가 논문 이해를 위해 먼저 지난 2020년 공개된 논문 내용을 간략히 다루고, 추가된 내용을 살펴보도록 하겠습니다. AlphaChip의 기반 연구: A graph placement methodology for fast...

Yeah, it's doing the festival circuit trying to drum up interest to get distribution. I hope it does, it's a fun sequel. Utter trash, sure, but a cool idea. And a lot better than the original.

I’m using Veroboard for my Spectrum project for that authentic 80s vibe. But you don’t have to. There are options like this if you want to interface a circuit with your Spectrum.

Oh, neat! Recreating the original on Veroboard is both awesome and a cool challenge. I know this is not useful for this project, but perhaps for something else later - here's a board I laid out. github.com/linker3000/Z...

A plug-in PCB for the ZX Spectrum that can be populated with your own project - linker3000/ZX-Spectrum-Breakout-Board